Librería Samer Atenea

Librería Samer Atenea

Librería Aciertas (Toledo)

Librería Aciertas (Toledo)

Kálamo Books

Kálamo Books

Librería Perelló (Valencia)

Librería Perelló (Valencia)

Librería Elías (Asturias)

Librería Elías (Asturias)

Donde los libros

Donde los libros

Librería Kolima (Madrid)

Librería Kolima (Madrid)

Librería Proteo (Málaga)

Librería Proteo (Málaga)

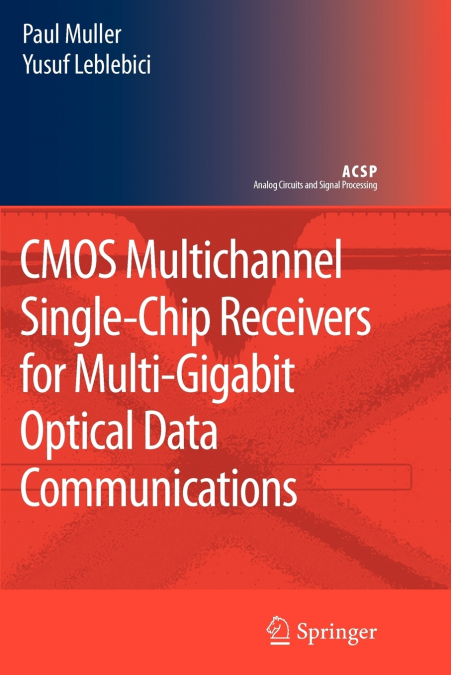

About the Authors. Foreword. Table of Contents. Constants, Symbols and Acronyms. CHAPTER 1 Introduction. CHAPTER 2 Integrated Photonic Systems. 2.1 Long-Haul Communication Links. 2.2 Metropolitan-Area Networks. 2.3 Local Area Networks and Short-Distance Interconnects. 2.4 Optical Backplane Technology. 2.5 Optical on-chip interconnects. CHAPTER 3 Basic Concepts. 3.1 Modulation of Optical and Electrical Signals. 3.2 NRZ Random Data. 3.3 Clock Recovery Basics. 3.4 Bit Error Rate. 3.5 System Bandwidth and Inter-Symbol Interference. 3.6 Amplitude Noise. 3.7 Jitter. 3.8 Multi-Channel Systems. 3.9 Definition of Transistor-Level Conventions. CHAPTER 4 System-Level Specifications. 4.1 Technology. 4.2 System-Level Requirements. 4.3 Receiver System Specifications. 4.4 Sub-Block Parameters. 4.5 Transimpedance Amplifier Analysis. 4.6 System Gain and Bandwidth Specifications. 4.7 Bit Error Rate Evaluation. 4.8 Block Specification Flow. CHAPTER 5 Pure Silicon Photodetector. 5.1 Photodetection. 5.2 PIN Photodiodes. 5.3 Avalanche Photodiodes. 5.4 Resonant Cavity Enhanced Detectors. 5.5 Conclusion. CHAPTER 6 Transimpedance Amplifier Design. 6.1 Principles of I-V Conversion. 6.2 Transimpedance Amplifier Topologies. 6.3 Specifications. 6.4 Transimpedance Amplifier Design. 6.5 Simulation Results. 6.6 Block Layout. 6.7 Measurement Results. 6.8 Discussion. CHAPTER 7 Limiting Amplifier Design. 7.1 Principles of Signal Limiting. 7.2 Simple Limiting Amplifier Topologies. 7.3 Bandwidth Enhancement in Limiting Amplifiers. 7.4 Specifications. 7.5 Inductorless Limiting Amplifier Design. 7.6 Design of an Inductive Peaking Limiting Amplifier. 7.7 Complete Limiting Amplifier. 7.8 Simulation Results. 7.9 Block Layout. 7.10 Measurement Results. 7.11 Discussion. CHAPTER 8 Clock and Data Recovery Circuit. 8.1 Clock Recovery Principles. 8.2 CDR Topologies. 8.3 Topology Discussion. 8.4 Specifications. 8.5 The Gated Oscillator Topology. 8.6 Statistical Modeling of the Gated Oscillator. 8.7 Time-Domain Modeling. 8.8 Transistor-Level Design. 8.9 Measurement Results. 8.10 Conclusion. CHAPTER 9 Conclusions. References.